# 12V单通道全桥驱动器

#### Chip description

GC8838 is a 12V DC motor driver chip that provides an integrated motor drive solution for cameras, consumer products, toys, and other low-voltage or battery-powered motion control applications. The chip is typically used to drive a single DC motor or two motors to drive a stepper motor.

GC8838 It can work on the power supply voltage of 0~ 12V, and can provide up to 1.5A continuous output current or 2.5A peak current, and the power consumption is less than 1uA in sleep mode.

GC8838 Has a PWM (IN/IN) input interface, compatible with industry standard devices, and has overtemperature protection function.

The chip also integrates undervo-Itage protection, output short circuit protection, overcurrent protection and other functions.

#### Chip features

H Bridge motor driver-load power supply voltage 0~ 12Vlow conduction impedance (HS+LS) 350m

1.5A continuous drive output current PWM (PH/EN) input mode

Compatible with 3.3V and 5V logic inputs

Built-in overtemperature protection

Built-in H-bridge power short circuit

protection, short ground protection

Low current sleep mode (nA class, when nSleep=0)

#### Chip application

camera

Digital single-lens reflex

(DSLR) lens Toy

robot technology

Shared bike locks

Water meter switch

armamentarium

| Product name | Package | Description Description |

|--------------|---------|-------------------------|

| GC8838       | DFN8    | 2*2mm e=0.5             |

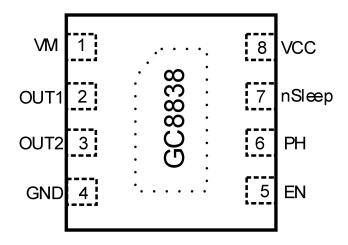

# Pin distribution diagram

# Pin description

| Pin number<br>DFN8 | Name of the tube | 1/0    | Description of the tubes and feet          |

|--------------------|------------------|--------|--------------------------------------------|

| 1                  | VM               | Power  | Power supply                               |

| 2                  | OUT1             | 0      | Output 1                                   |

| 3                  | OUT2             | 0      | Output 2                                   |

| 4                  | GND              | ground | The earth                                  |

| 5                  | EN               | I      | Enable input (see logic table for details) |

| 6                  | РН               | I      | Phase input (see logic table for details)  |

| 7                  | nS1eep           | I      | Power saving mode input,<br>low effective  |

| 8                  | VCC              | Power  | 3.3V or 5V logic power su-<br>pply         |

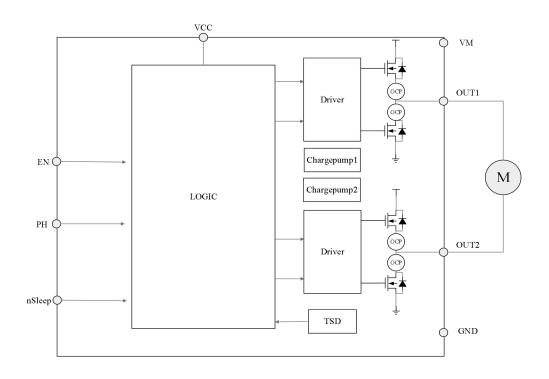

# Internal block diagram

Figure 1 GC8838 Internal block diagram

# Extreme parameters (T = 25 unless otherwise specified)

| Parameter                                  | Symbol | Parameter range      | Uni t |

|--------------------------------------------|--------|----------------------|-------|

| Logic voltage range                        | VCC    | -0. 3 <sup>~</sup> 7 | V     |

| Load voltage                               | VM     | 0~16                 | V     |

| Control the input vo-<br>Itage range       | EN, PH | -0.5 <sup>~</sup> 7  | V     |

| A constant current for a long time         | Ion    | ±1.5                 | A     |

| Drive peak current                         | Imax   | ±2.5                 | A     |

| Junction temperature                       | Tjmax  | -40~150              | °C    |

| Storage temperature                        | Tstg   | -60 <sup>~</sup> 150 | °C    |

| Electrostatic protection (human body mode) | ESD    | ±5000                | V     |

Electrical parameters (T=25, VCC=3V, VM=12V in general without special note) Recommended working environment: (no other description, T=25)

| Param<br>eter               | Symbol                                        | Test condi-<br>tion | Least<br>val ue | Representative value | Crest<br>value | Uni<br>t |

|-----------------------------|-----------------------------------------------|---------------------|-----------------|----------------------|----------------|----------|

| Logic power supply          | VCC                                           |                     | 2.0             |                      | 7              | V        |

| Power supply for the Load   | VM                                            |                     | 0               |                      | 12             | V        |

| Out<br>put                  | ${ m I}_{ m out}$                             |                     | 0               |                      | 1.5            | A        |

| External PWM fr-<br>equency | $\mathrm{f}_{\scriptscriptstyle\mathrm{PWM}}$ |                     | 0               |                      | 400            | kH<br>Z  |

| Working temp-<br>erature    | Ta                                            |                     | -40             |                      | 85             | °C       |

Electrical characteristics: (no other description, T=25, VCC=3V, VM=12V)

| Parameter                                                           | Symbol                                   | Test condi -<br>tion                      | Least<br>value | Representative<br>value | Crest<br>val ue | Un<br>i t |

|---------------------------------------------------------------------|------------------------------------------|-------------------------------------------|----------------|-------------------------|-----------------|-----------|

| VCC operating current 1                                             | $I_{	ext{vcc1}}$                         | Not<br>have<br>PWM                        |                | 368                     | 450             | u<br>A    |

| The operating current of VCC is 2                                   | $\mathrm{I}_{	ext{vcc2}}$                | PWM<br>50<br>kHz                          |                | 0.68                    | 1.0             | m<br>A    |

| VCC standby cur-<br>rent                                            | $I_{	ext{vccq}}$                         | nSIeep=0 power<br>saving mode             |                | 40                      | 80              | n<br>A    |

| VM working current<br>1                                             | ${ m I}_{{\scriptscriptstyle { m VM1}}}$ | Not<br>have<br>PWM                        |                | 214                     | 550             | u<br>A    |

| VM working current 2                                                | $I_{	ext{VM}2}$                          | 50<br>KHz<br>PWM                          |                | 0.58                    | 0.90            | m<br>A    |

| VM working current<br>2                                             | $I_{\text{VMQ}}$                         | nSIeep=0 power<br>saving mode             |                | 1.3                     | 20              | n<br>A    |

| Output H, bridge param                                              | neters                                   |                                           |                |                         |                 |           |

| Bridge conduction<br>resistance of upper                            | $R_{\rm dsON1}$                          | I <sub>°</sub> =500mA;<br>T=25°           |                | 350                     | 450             | m<br>Ω    |

| arm + lower arm                                                     | $R_{\rm ds0N2}$                          | $I_{\circ}$ =500mA; T= $125^{\circ}$      |                | 530                     | 700             | m<br>Ω    |

| Off-state leakage<br>current                                        | $I_{ m OFF}$                             | Y O U U T T T T T T T T T T T T T T T T T | -10            |                         | 10              | u<br>A    |

| Logical input feet (Ph                                              | I, EN, nSI                               | eep)                                      | I              |                         |                 |           |

| The logic is rever-                                                 |                                          | P<br>H<br>,<br>E<br>N                     |                | 1. 28                   |                 | v         |

| sed from high to low<br>at the voltage point                        | $V_{\scriptscriptstyle \mathrm{IL}}$     | n<br>S<br>1<br>e<br>e<br>p                |                | 1. 28                   |                 | V         |

| The logic is rever-<br>sed from low to high<br>at the voltage point | $V_{{\scriptscriptstyle \mathrm{IH}}}$   | P<br>H<br>E<br>N                          |                | 1. 58                   |                 | V         |

|                                                                     |                                          | n                                         |                |                         |                 | V         |

|                                       |                                         | S                                              |      |       |     |        |

|---------------------------------------|-----------------------------------------|------------------------------------------------|------|-------|-----|--------|

|                                       |                                         | 1<br>e<br>e<br>p                               |      | 1. 58 |     |        |

|                                       |                                         | P<br>H<br>E<br>N                               |      | 300   |     | m<br>V |

| Reverse hyster-<br>esis               | V <sub>HY</sub>                         | n<br>S<br>1<br>e<br>e<br>p                     |      | 300   |     | m<br>V |

| Low input current at the logic level  | ${ m I}_{{\scriptscriptstyle { m IL}}}$ | v<br>i                                         | -5   |       | 5   | u<br>A |

| High input current                    | ${ m I}_{{\scriptscriptstyle { m IH}}}$ | Vin = 3.3V, EN,<br>PH pins                     |      | 30    |     | u<br>A |

| l ogi c                               |                                         | Vin = 3.3V, nS-<br>leep pin                    |      | 30    |     | u<br>A |

| Pull-down resi-<br>stor               | $R_{pd}$                                | PH, EN,<br>nSleep                              |      | 100   |     | k<br>Ω |

| Guard circuit                         | I                                       | I                                              |      | I     | I   | ı      |

| Over temperature protection           | TSD                                     | Temperatur<br>e rise                           | 155  | 169   | 180 | ъ      |

| Overtemperature protection hysteresis | Δ TSD                                   |                                                |      | 26    |     | е      |

| Undervol tage prote-<br>ction         | V <sub>UVLO</sub>                       | Sour<br>ce<br>VCC                              |      | 1. 9  |     | V      |

| Undervol tage prote-<br>ction         | $\Delta V_{\text{UVLO}}$                | Sour<br>ce<br>VCC                              |      | 1.8   |     | V      |

| Overcurrent protec-                   | $I_{ocp}$                               | Arm<br>brid<br>ge                              |      | 3. 0  |     | A      |

| tion                                  | _ our                                   | Lower arm<br>bridge                            |      | 3.0   |     | A      |

| Overcurrent protection lag            | $T_{	ext{DEG}}$                         | Overcurrent protection hysteresis time         |      | 1.5   |     | u<br>S |

| Overcurrent protection recovery time  | Tretry                                  | Overcurrent pr-<br>otection recov-<br>ery time | V1 2 | 1.5   |     | m<br>S |

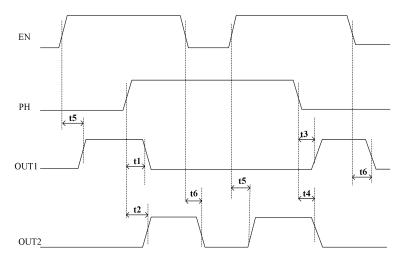

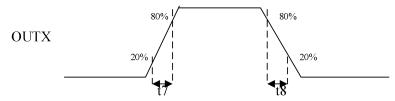

#### Time series parameters and curves

TA =  $25^{\circ}$  C, VCC = 5 V, RL =  $20^{\circ}$   $\Omega$

| Parameter    | Condition                                 | Sco       | Uni t    |        |  |

|--------------|-------------------------------------------|-----------|----------|--------|--|

| Pai allietei | Condition                                 | Mi ni mum | Maxi mum | OIII t |  |

| t1           | Delay time, PHASE high to OUT1<br>low     |           | 160      | ns     |  |

| t2           | The delay time is PHASE high to OUT2 high |           | 200      | ns     |  |

| t3           | The delay time is PHASE low to OUT1 high  |           | 200      | ns     |  |

| t4           | The delay time is PHASE low to OUT2 low   |           | 160      | ns     |  |

| t5           | The delay time is high for ENBL and OUTx  |           | 200      | ns     |  |

| t6           | The delay time is low for ENBL and OUTx   |           | 160      | ns     |  |

| t7           | Increase the output rise time             | 30        | 188      | ns     |  |

| t8           | Reduce the time of output de-<br>cline    | 30        | 188      | ns     |  |

|              | Wake up time, nSLEEP to output open       |           | 30       | us     |  |

Figure 2 GC8838 Input and output time parameters 1

Figure 3 GC8838 Input and output time parameters 2

#### functional description

#### Bridge arm control

GC8838 Controlled by the PWM input interface, also known as IN/IN input mode, its control truth table is as follows:

| nS1eep | РН  | EN  | OUT1 | OUT2 | Function       |

|--------|-----|-----|------|------|----------------|

| 0      | X   | X   | Z    | Z    | Dormancy       |

|        |     |     |      |      | Stop a vehicle |

| 1      | X   | 0   | L    | L    | by applying    |

|        |     |     |      |      | the brake      |

| 1      | 1   | 1   | ī    | Н    | Opposite dir-  |

| 1      | 1   | 1   | L    | 11   | ection         |

| 1      | 0 1 | 0 1 | Н    | ī    | Forward dire-  |

| 1      | U   | 1   | 11   | L    | ction          |

#### Output drive

The output drive upper and lower tubes use NMOS power tubes, and the built-in charge pump circuit, the sum of the internal resistance of the upper and lower tubes is as low as 400 m

### Sleep patterns

When the nSleep is high, the chip works normally.

When the nSleep is low, the chip enters a low-power sleep mode, which consumes power at the nA level and is suitable for low-power systems. The nSleep has a built-in 100k resistor that pulls down to ground, and the default sleep mode is when the external input is suspended.

#### Input foot

The input foot has a 100K resistor pull-down and is set to low level input by default. **guard circuit**

Over temperature protection

When the chip junction temperature exceeds 169, the overtemperature protection circuit is activated, shutting off all output transistors. When the temperature drops by a hysteresis temperature of 26 and reaches 143, all output transistors resume operation; since overtemperature protection only activates when the chip junction temperature exceeds the set value, it does not guarantee that the product will be protected from damage with this circuit alone, so the chip is equipped with short-circuit overcurrent protection.

Short circuit protection OCP

The chip includes overcurrent protection circuits in each drive transistor of the H bridge. When any drive transistor detects a current exceeding IOCP and lasting longer than the hysteresis time TDEG (1.4 us), all drive transistors will turn off. After Tretry time (1.5 ms), the drive transistors will automatically attempt to return to normal operation. If abnormal currents persist, the shutdown-recovery-shutdown process will be repeated.

Overcurrent protection is generally designed to protect against abnormal conditions that could cause the chip to burn out. For example, when the upper arm bridge of OUT1 is conducting, if OUT1 abnormally touches ground, or when the lower arm bridge of OUT1 is conducting, OUT1 abnormally shorts to the power supply. This type of protection is also known as short-to-ground and short-to-power protection.

#### work pattern

GC8838 Enter sleep mode when the nSleep is low, in sleep mode H, all bridges are turned off, output high resistance state, most of the chip circuit is turned off, and enter power saving mode.

| Pattern | Condition | H bridge |

|---------|-----------|----------|

| Work    |           | Work     |

|                   | nSleep=H                         |                                  |

|-------------------|----------------------------------|----------------------------------|

| Sleep patterns    | nSleep=L                         | Turn-off                         |

| Failuma dataatian | Over temperature, under pressure | Turn-off                         |

| Failure detection | OCP                              | Shut down-restore-shut down mode |

http://www.xinmaizj.com

V1.3

Page 6 of 8

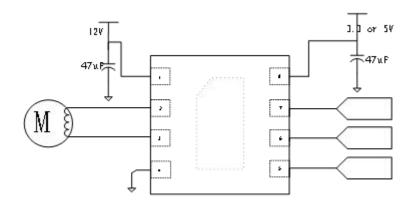

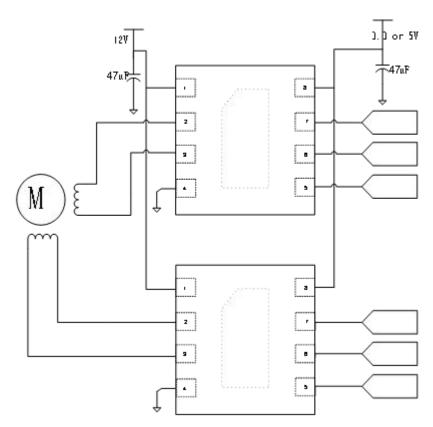

## Typical application circuit diagram

Figure 4 GC8838 Typical application schematic

GC8838 Drive DC motor diagram

Two GC8838 drive stepper motor diagram

VCC, the bypass capacitor connection of VM should be as close as possible to the chip VCC, VM foot. When the load power supply exceeds 12V, it is recommended to increase the VM bypass capacitor greater than 56uF.

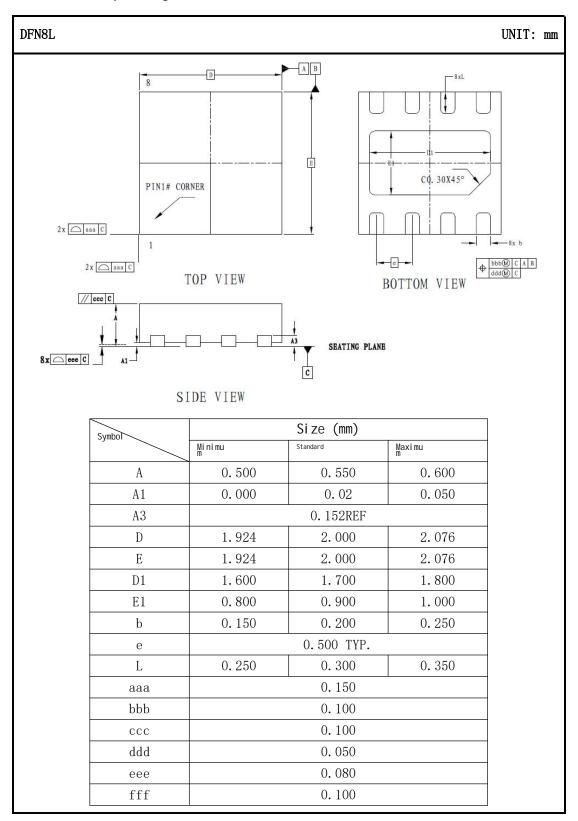

## Encapsulate the shape diagram