#### description

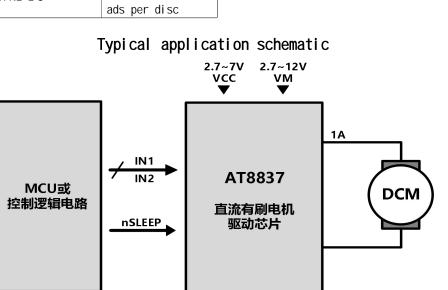

AT8837 provides an integrated motor driver solution for low-voltage applications such as cameras, smart locks, and toys, or battery-powered products. AT8837 can drive a brushed DC motor or inductive loads like solenoids, offering up to 1A of drive current. The device operates within a power supply voltage range of 2.7-12V and includes comprehensive protection features such as overcurrent, short circuit, overtemperature, and undervoltage lockout.

AT8837 It has a PWM (IN1/IN2) input interface.

AT8837 Provide a DFN-8 (2mm\*2mm) package with exposed pads, and it is lead-free product, which meets the environmental protection requirements.

#### Appl

- Camera **y**

- consumer

- products

- ∎ toys

- Roboti

- C SM-

- art

- ∎ door

#### Model selection

| Order number | Package  | Pack             |  |

|--------------|----------|------------------|--|

| AT8837       | DFN2*2-8 | Strips, 3000 be- |  |

| 110057       |          | ads per disc     |  |

Low voltage H bridge motor drive chip characteristic

Independent H-bridge drive circuit Drive a DC brushed motor or other inductive load Low RDS (ON) resistance, 1.05 (HS + LS) Continuous drive output of 1A Wide voltage supply range, 2.7-12V nSLEEP Low power sleep mode controlled by the pin overcurrent protection Overtemperature shutdown circuit short-circuit protection Under-voltage lockout protection **Packaging form**

**DFN-8** with PAD

# Version update log

| Date    | Edition | Content                                                                                                                                                                                                                                                                           |

|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2018.04 | V1.0    | Initial version                                                                                                                                                                                                                                                                   |

| 2018.09 | V1.1    | Power supply voltage lower limit correction                                                                                                                                                                                                                                       |

| 2018.12 | V1.2    | Correction of voltage rating of power filter capacitor                                                                                                                                                                                                                            |

| 2020.03 | V1.3    | <ol> <li>Modify the upper limit of power supply<br/>voltage;</li> <li>Add packaging information;</li> <li>Increase the thermal resistance paramet-<br/>er;</li> <li>Add a table of temperature characterist-<br/>ics for test waveforms and conduction impe-<br/>dance</li> </ol> |

| 2020.09 | V1.4    | Modify the POD size of the package                                                                                                                                                                                                                                                |

Hangzhou Zhongke Microelectronics Co., LTD Low voltage H bridge motor drive chip

The working limit of the circuit is at TA =  $25^{\circ}$  C

| Parameter                     | Symbol              | Condi ti on           | Scope       | Uni t |

|-------------------------------|---------------------|-----------------------|-------------|-------|

| Motor power supply voltage    | VM                  |                       | -0.3 – 15   | V     |

| Continuous output current     | Iout                |                       | ±1          | А     |

| Instantaneous peak current    | I <sub>PEAK</sub>   | Internal restrictions | >1.5        | А     |

| Logic power supply voltage    | VCC                 |                       | -0.3 to 7   | V     |

| Logic input voltage           | V <sub>IN</sub>     |                       | -0.5 to VCC | V     |

| Operating ambient temperature | T <sub>A</sub>      |                       | -40 to 85   | °C    |

| Maximum junction temperature  | T <sub>J(max)</sub> |                       | 150         | °C    |

| Storage temperature           | Tstg                |                       | -55 to 150  | °C    |

### Thermal resistance characteristic at Ta = 25° C

| Heat metering                                                          | DFN<br>8PINS | Uni t |

|------------------------------------------------------------------------|--------------|-------|

| JA-Thermal resistance coefficient (*) from silicon core to environment | 50           | °C/W  |

(\*) The thermal resistance coefficient of silicon core to the environment under natural convection is obtained by actual test on a JEDEC standard high K circuit board specified in JESD51-7, and environmental conditions are as described in JESD 51-2a.

#### Recommended working conditions at $TA = 25^{\circ} C$

| Parameter                  | Symbol        | Minimum | Typi cal<br>case | Maxi mum | Uni t |

|----------------------------|---------------|---------|------------------|----------|-------|

| Motor power supply voltage | VM            | 2.7     | -                | 12       | V     |

| Logic power supply voltage | VCC           | 2.7     | -                | 5.25     | V     |

| Continuous output current  | Iout          | 0       | -                | 0.8      | А     |

| Enter the PWM frequency    | $f_{\rm PWM}$ | 0       | -                | 250      | kHz   |

(1) All voltage values are based on the ground port as the potential zero point.

(2) When the chip works with large current, do a good job of chip heat dissipation.

(3) The performance of the chip is not guaranteed when it operates under conditions other than those recommended.

(4) When the chip works beyond the circuit limit, it may cause permanent damage to the device.

(5) If the chip is placed for a long time beyond the operating limit of the circuit, it may affect the reliability of the device.

| ł | lang | jzhou | Zhongl | ke | Mi croel | lectro | ni cs | Co. , | , L | .TD |

|---|------|-------|--------|----|----------|--------|-------|-------|-----|-----|

|   |      |       |        |    |          |        |       |       |     |     |

Low voltage H bridge motor drive chip

**AT8837**

|                       | Parame                             | tTA = 25° C, VM= 5 V,<br>Test co-  |         |                  |          | llni     |

|-----------------------|------------------------------------|------------------------------------|---------|------------------|----------|----------|

|                       | ter                                | ndi ti on                          | Minimum | Typi cal<br>case | Maximum  | Uni<br>t |

| Power su              | ppl y                              |                                    |         |                  |          |          |

| I <sub>VM</sub>       | VM Static operating<br>current     |                                    |         | 0.3              | 0.8      | m<br>A   |

| I <sub>VMQ</sub>      | VM sleep current                   | nSLEEP = 0                         |         | 50               | 100      | n<br>A   |

| I <sub>VCC</sub>      | VCC static operating current       |                                    |         | 0.8              | 1.5      | m<br>A   |

| Ivccq                 | VCC sleep working cur-<br>rent     | nSLEEP = 0                         |         | 0.3              | 1        | uA       |

| Logical i             | nput                               |                                    |         |                  |          |          |

| V <sub>IL</sub>       | Low voltage for logical<br>input   |                                    |         |                  | 0.8      | V        |

| V <sub>IH</sub>       | High voltage for logical<br>input  |                                    | 2.0     |                  |          | V        |

| V <sub>HYS</sub>      | Logical input hystere-<br>sis      |                                    |         | 0.24             |          | V        |

| I <sub>IL</sub>       | Logic input current _<br>low level | $V_{IN} = 0$                       |         |                  | 1        | u<br>A   |

| Logic input current _ | IN1, IN2                           |                                    | 30      |                  | u<br>A   |          |

| I <sub>IH</sub>       | high level                         | nSLEEP                             |         | 30               |          | u<br>A   |

| R <sub>PD</sub>       | Enter internal pull-down           | nSLEEP                             |         | 100              |          | KΩ       |

|                       | resistance                         | IN1, IN2                           |         | 100              |          | KΩ       |

| H bridge              | FETs                               |                                    |         |                  |          |          |

| R <sub>DS(ON)</sub>   | High side FET on-<br>resistance    | $I_0 = 200 mA$                     |         | 700              |          | 0        |

| KDS(ON)               | Low side FET on-<br>resistance     | $I_0 = 200 \text{mA}$              |         | 350              |          | mΩ       |

| I <sub>off</sub>      | Output turn-off leakage<br>current |                                    | -1      |                  | 1        | u<br>A   |

| Guard cir             | rcui t                             |                                    |         |                  |          |          |

| I <sub>OCP</sub>      | Overcurrent protection threshold   |                                    | 1.2     | 1.35             |          | A        |

| t <sub>DEG</sub>      | OCP anti-shake delay               |                                    |         | 3                |          | us       |

| T <sub>retry</sub>    | OCP reboot time                    |                                    |         | 1.3              |          | ms       |

| T <sub>TSD</sub>      | Over temperature thre-<br>shold    | Chip internal junction temperature | 150     | 160              | 180      | °C       |

| V <sub>UVLO</sub>     | VCC under-voltage lock<br>value    | VCC rise                           |         | 2.6              |          | V        |

| V <sub>UVLO HYS</sub> | VCC under-voltage hys-<br>teresis  |                                    |         | 100              |          | m<br>V   |

| Resting s             | state                              | 1                                  | 1       | 1                | <u>I</u> |          |

| twake                 | Sleep wake time                    | Pull up nSLEEP to bridge H         |         | 35               |          | us       |

www.icofchina.com

Page 4 of 16

AT8837-S402-V1.4

Low voltage H bridge motor drive chip

837

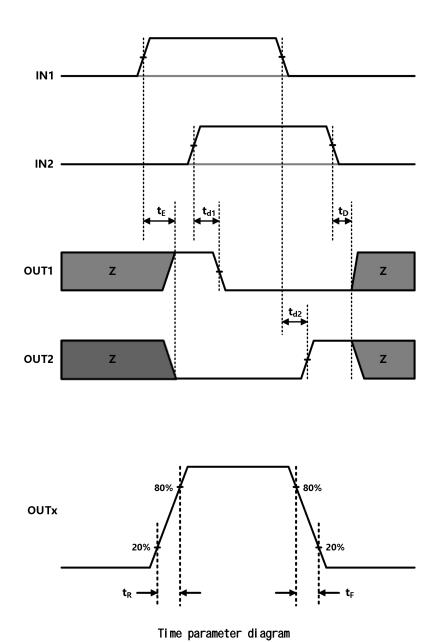

| $t_{\rm E}$       | Output enable time                                        | Output enable time               | 325 | 500 | ns |

|-------------------|-----------------------------------------------------------|----------------------------------|-----|-----|----|

| t <sub>D</sub>    | Output turn-off time                                      | Output disable time              | 200 | 500 | ns |

| t <sub>d1</sub>   | Input changes to output with<br>low delay                 | Delay time, IN2 high to OUT1 low | 300 | 500 | ns |

| t <sub>d2</sub>   | The input change takes a long<br>time to go to the output | Delay time, IN1 low to OUT2 high | 400 | 500 | ns |

| t <sub>R</sub>    | Rise time                                                 | $22\Omega$ to GND, 20% to 80%    | 20  | 180 | ns |

| t <sub>F</sub>    | Drop-out time                                             | $22\Omega$ to GND, 80% to 20%    | 5   | 180 | ns |

| t <sub>DEAD</sub> | Dead zone time                                            |                                  | 205 |     | ns |

# Typical work characteristic curve

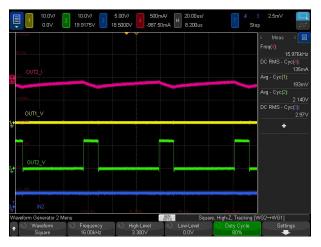

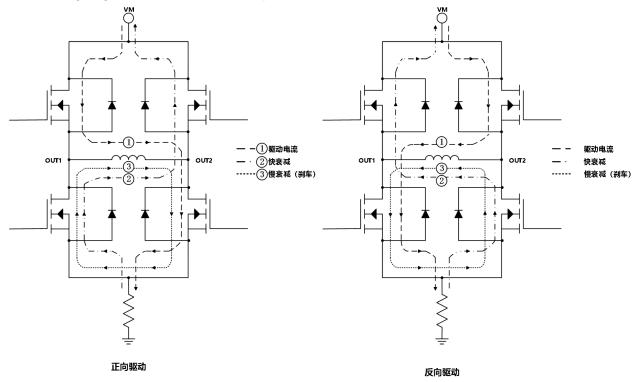

20% duty cycle, positive

20% duty cycle, reverse

50% duty cycle, positive

50% duty cycle, reverse

Low voltage H bridge motor drive chip

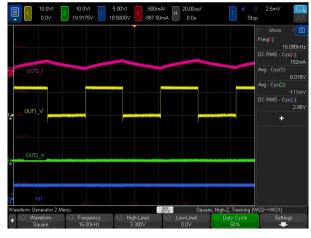

# Module function description

AT8837 provides an integrated drive solution for single brushed DC motors or inductive loads such as solenoids. The chip internally integrates a H-bridge power output module, delivering a peak current output of 1A. AT8837 operates within a normal voltage range of 2.7 to 12V. By pulling down the nSLEEP pin, AT8837 can achieve low-power sleep mode.

The chip integrates the power tube and its control circuit, reduces the number of peripheral devices, and has complete protection functions such as overcurrent, short circuit, overheating and undervoltage lock.

functional block diagram

# H bridge control logic

The input pins IN1 and IN2 control the enable and current direction of the H bridge. The following table shows the logical relationship between them.

| nSLEEP | IN1 | IN2 | OUT1 | OUT2 | Function (DC mo-<br>tor)             |

|--------|-----|-----|------|------|--------------------------------------|

| 0      | Х   | Х   | Z    | Z    | Dormancy                             |

| 1      | 0   | 0   | Z    | Z    | GI i ssade                           |

| 1      | 0   | 1   | L    | Н    | Reversal                             |

| 1      | 1   | 0   | н    | L    | Corotation                           |

| 1      | 1   | 1   | L    | L    | Stop a vehicle by applying the brake |

#### H Bridge control logic table

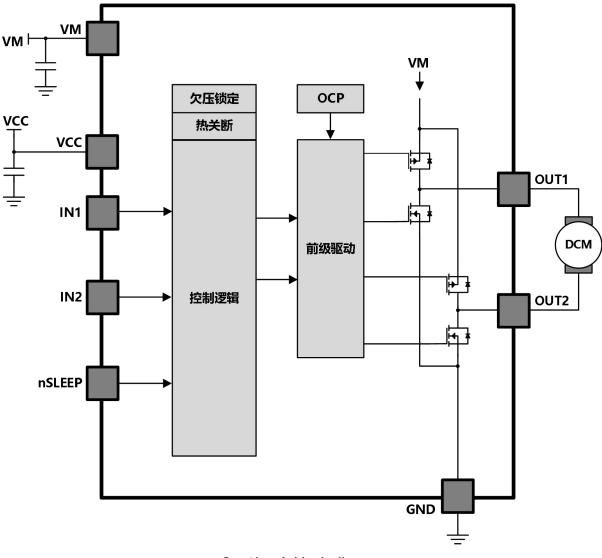

The logic input can also use PWM control to achieve speed regulation. When a PWM wave controls a coil, the drive current is interrupted, and due to the inductive characteristics of the motor, the motor coil must continue to conduct. To operate the motor coil to continue conducting, the H-bridge can operate in two different states: fast decay or slow decay. In fast decay mode, the H-bridge turns off, and the freewheeling current flows through the body diode; in slow decay mode, the ends of the motor coil are short-circuited.

When PWM control is used in fast attenuation mode, the PWM signal controls one INx pin while the other pin remains low; when used in slow attenuation mode, one of the pins remains high.

| IN1 | IN2 | Function                |

|-----|-----|-------------------------|

| PWM | 0   | Forward PWM, fast decay |

| 1   | PWM | Forward PWM, slow decay |

| 0   | PWM | Reverse PWM, fast decay |

| PWM | 1   | Reverse PWM, slow decay |

#### PWM controls motor speed

The following figure shows the current path in different drive and attenuation modes.

Drive and decay mode

#### Overcurrent protection (OCP)

On each FET, there is a current detection circuit. When the current exceeds the set threshold and persists for more than the OCP anti-flicker time tDEG, all FETs in the H-bridge turn off. After a period of overcurrent reset tRETRY, the H-bridge will open again. If the overcurrent is cleared, the H-bridge resumes normal operation; if the overcurrent persists, the aforementioned action repeats.

Overcurrent protection is triggered if the upper and lower pipes of H bridge are short-circuited to ground, to VM, or to the output.

#### Overtemperature protection (TSD)

If the junction temperature exceeds the safety threshold, all FETs in the H bridge will be turned off. After the junction temperature drops to a certain value, the chip will automatically return to normal operation.

#### Under-voltage lockout protection (UVLO)

If the voltage on the VCC pin is below the undervoltage lockout threshold, all FETs in the internal H-bridge are turned off. When the VCC rises above the undervoltage lockout threshold, the chip automatically returns to normal operation.

#### Device protection threshold

| Abnormal conditions                            | Trigger conditions           | H bridge | Recover                 |  |  |

|------------------------------------------------|------------------------------|----------|-------------------------|--|--|

| VCC Under-voltage Lockout<br>Protection (UVLO) | VCC < 2.55V                  | Turn-off | VCC > 2.65V             |  |  |

| Overcurrent, short circuit protection (OCP)    | I <sub>OUT</sub> > 1.2A(MIN) | Turn-off | After 1.2ms             |  |  |

| Thermal shutdown (TSD)                         | T <sub>J</sub> > 160 °C(MIN) | Turn-off | $T_J < 140 \ ^{\circ}C$ |  |  |

| Abnormal condition table                       |                              |          |                         |  |  |

#### Device function mode

nSLEEP When the nSLEEP pin is input at a low level, the device enters low-power sleep mode. After entering low-power sleep mode, the H-bridge of the device is turned off and all logic inputs are ignored; when the nSLEEP pin is input at a high level, the chip returns to normal operation.

It is recommended to pull all input pin levels to low level when entering low power sleep mode in order to further reduce chip power consumption.

| Pattern               | Condi ti on                     | H bridge     |

|-----------------------|---------------------------------|--------------|

| Regular work          | nSLEEP = 1                      | Regular work |

| SLeep mode            | nSLEEP = 0                      | Turn-off     |

| An exception occurred | Meet any exceptional conditions | Turn-off     |

|                       | Frankler will take              |              |

Function mode table

www.icofchina.com

Low voltage H bridge motor drive chip

# Information on circuit applications

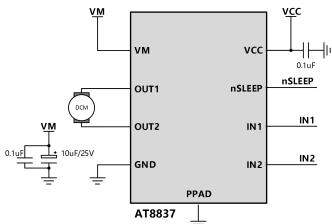

Brushed DC motor drive

#### Typical design requirements

| Design value                                 | Refer to         | Example values |

|----------------------------------------------|------------------|----------------|

| Motor power supply voltage                   | VM               | 12V            |

| Logic power supply voltage (only AT<br>8837) | VCC              | 5V             |

| Target current RMS                           | I <sub>OUT</sub> | 0.5A           |

Typical application

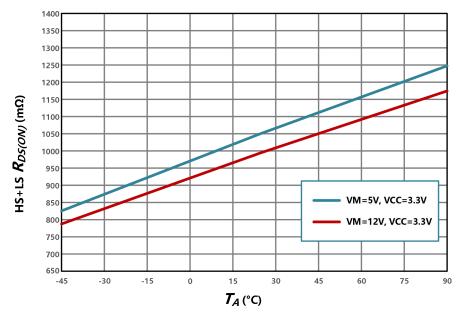

## Detailed design process power dissipation

The power consumption of AT8837 is mainly on the impedance RDS (ON) of the FET in the H bridge.

The average power consumption can be roughly estimated as:

$$P_{TOT} = R_{DS(ON)} \times (I_{OUT(RMS)})^2$$

In the formula

PTOT is the total power dissipation;

RDS (ON) is the total conduction impedance (HS+LS);

IOUT (RMS) is the effective value of the output current.

The maximum power consumption that the device can withstand depends on the ambient temperature and heat dissipation.

Note: RDS (ON) increases with temperature, so power consumption increases as the device temperature increases.

AT8837 Built-in thermal shutdown protection, when the junction temperature reaches about 160  $^{\circ}$  C, the H bridge will be shut down until the temperature drops to a safe range.

The chip is easy to touch and turn off because of high power consumption, insufficient heat dissipation or high ambient temperature.

#### Power and input pins

The VM does not have an undervoltage lockout function (UVLO). As long as the VCC is greater than 2.7V, the internal circuit logic will remain in operation, which means that the VM supply voltage can be as low as OV, but the load cannot be fully driven in the low VM state.

Regardless of whether the VCC and VM ports are connected to the power supply, the input pins should be configured under recommended operating conditions. There is no leakage current path between the input pins and the power supply. Each input pin has a pull-down resistor (about 100k

www.icofchina.com

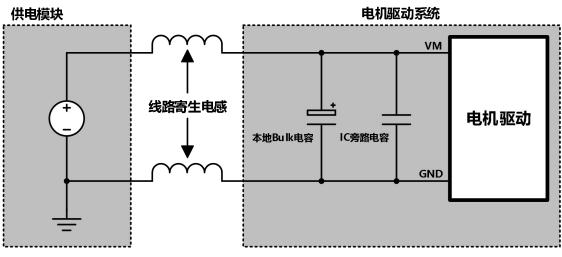

## Power supply recommendations

Both the VM and the VCC should be connected to a  $0.1 \mu$  ceramic capacitor to ground, and the capacitor should be placed as close to the device as possible.

The right Bulk capacitor is the key to motor drive system design. Generally, the larger the Bulk capacitor, the better the effect, but it also brings the cost and PCB size increase.

The capacitance value required depends on the following factors:

Maximum current required by the motor system The capacitance of the power supply and its ability to supply current The parasitic inductance between the power supply and the motor system Acceptable voltage ripple Type of motor used (brushed, brushless, stepper) Motor braking method

The inductance between the power supply and the motor system limits the rate of change of output current. If the capacitance value of the local Bulk capacitor is set too low, the system voltage will fluctuate when encountering high currents or sudden changes in motor load; if sufficient Bulk capacitors are used, the voltage can remain stable and provide a large current to the motor.

Example configuration of a motor drive system powered by an external power supply

The voltage rating of bulk capacitor should be slightly higher than the working voltage to prevent the motor from overvoltage to the power supply.

LTD Low voltage H bridge motor drive chip

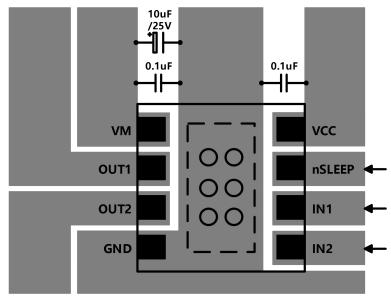

# Map layout notes

The PCB should be covered with a large area of copper, and the power and ground lines should have enough width. In order to optimize the electrical characteristics and thermal performance of the circuit, the chip should be directly attached to the PCB, copper covered.

For VM and VCC ports, use a ceramic capacitor with low ESR to connect to ground. The recommended capacitance is 0.1uF. These capacitors should be placed as close as possible to the VM and VCC pins and connected through a wide enough ground wire and GND pin.

In order to avoid the capacitance coupling problem caused by high speed dV/dt transformation, the output end of the drive circuit and the input end of the logic control are isolated by ground wire.

#### Ground wire setting

All ground lines in the chip should be connected together, and the connection should be as short as possible. One optimization scheme is to lay the ground lines under the device, in a star pattern.

A piece of copper with the right size is placed on the back of the PCB to improve circuit performance.

#### Map example

Simplified map example

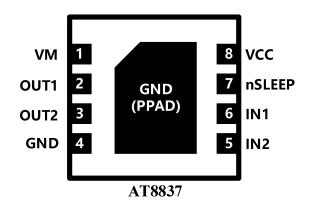

# Pin definition

#### Pin list

| 131         |            |          |                        |                                                                                                                                             |

|-------------|------------|----------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>name | Pin number | Pin type | Pin descri-<br>ption   | External components or connections                                                                                                          |

| GND         | 4          | PWR      | Chip it                | All GND pins and bare pads of the chip                                                                                                      |

| PPAD        | -          | PWR      | Chip It                | should be connected to the power ground.                                                                                                    |

| VM          | 1          | PWR      | Motor power<br>supply  | Connect an external 0.1uF ceramic capac-<br>itor to ground for bypass.                                                                      |

| vcc         | 8          | PWR      | Logic power<br>supply  | Connect an external O.1uF ceramic capac-<br>itor to ground for bypass.                                                                      |

| NC          | -          | -        | -                      | The pins are suspended.                                                                                                                     |

| IN1         | 6          | I        | Control logic<br>input |                                                                                                                                             |

| IN2         | 5          | I        | Control logic<br>input |                                                                                                                                             |

| nSLEEP      | 7          | I        | Sleep mode<br>input    | Logic high level, the chip works normal-<br>ly; logic low level, the chip enters low<br>power sleep mode. Built-in pull-down re-<br>sistor. |

| OUT1        | 2          | 0        | H bridge out-<br>put 1 | Connect to the motor soil                                                                                                                   |

| OUT2        | 3          | 0        | H bridge out-<br>put 2 | Connect to the motor coil.                                                                                                                  |

| 微 | 象 | ß | Ę |

|---|---|---|---|

|   |   |   |   |

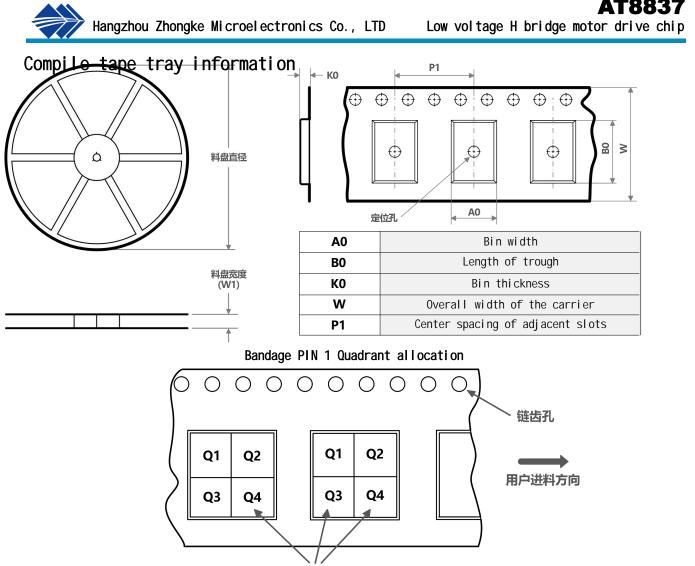

| D<br>e<br>v<br>i<br>c<br>e | Packag<br>e<br>Typ<br>e | Package<br>Characteristic | Number<br>of<br>pins | SP<br>Q | Chargi ng<br>tray<br>Di ameter<br>(mm) | Chargi ng<br>tray<br>Wi dth<br>(mm) | (m<br>m) | (m<br>m) | ،<br>(m<br>m) | '<br>(m<br>m) | (m<br>m) | Pin 1<br>Quadrant |

|----------------------------|-------------------------|---------------------------|----------------------|---------|----------------------------------------|-------------------------------------|----------|----------|---------------|---------------|----------|-------------------|

| AT<br>88<br>37             | DFN                     | -                         | 8                    | 3000    | 178                                    | 8                                   | 2        | 2        | 0.75          | 4             | 8        | Q2                |

Band material tray packaging size

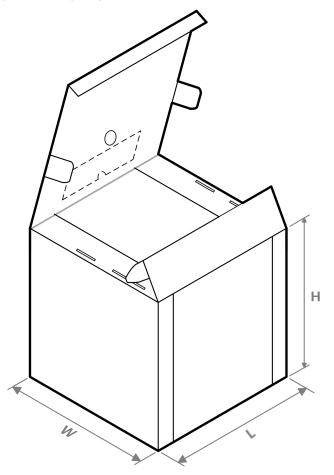

| De<br>vi<br>ce | Packagi ng<br>type | Packaging identi-<br>fication | Number of<br>pins | SP<br>Q | Length<br>(mm) | Width<br>(mm) | Altitude<br>(mm) |

|----------------|--------------------|-------------------------------|-------------------|---------|----------------|---------------|------------------|

| AT<br>883<br>7 | DFN                | -                             | 8                 | 3000    | 210            | 210           | 210              |

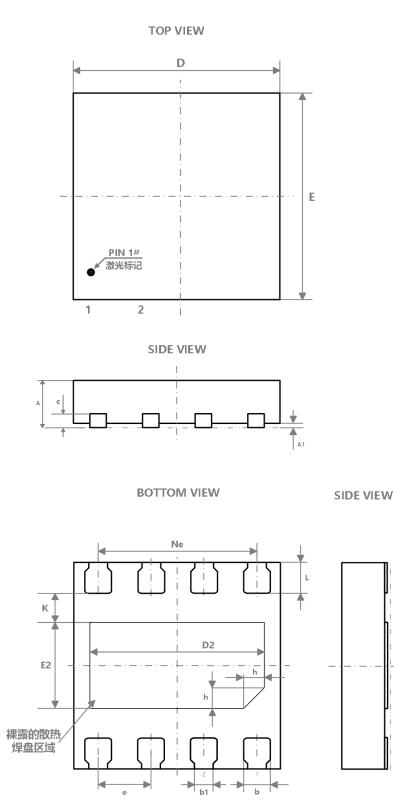

# Package information

| Symbol       | Millimetre (mm) |             |      |  |  |  |  |  |

|--------------|-----------------|-------------|------|--|--|--|--|--|

| - O'Jiiibo'i | MIN             | MIN NOM MAX |      |  |  |  |  |  |

| А            | 0.50            | 0.55        | 0.60 |  |  |  |  |  |

| A1           | 0               | 0.02        | 0.05 |  |  |  |  |  |

| b            | 0.20            | 0.25        | 0.30 |  |  |  |  |  |

| b1           | 0.11            | 0.16        | 0.21 |  |  |  |  |  |

| С            | 0.10            | 0.15        | 0.20 |  |  |  |  |  |

| D            | 1.90            | 2.00        | 2.10 |  |  |  |  |  |

| D2           | 1.60            | 1.70        | 1.80 |  |  |  |  |  |

| е            | 0.50BSC         |             |      |  |  |  |  |  |

| Ne           |                 | 1.50BS0     | 2    |  |  |  |  |  |

| E            | 1.90            | 2.00        | 2.10 |  |  |  |  |  |

| E2           | 0.80            | 0.90        | 1.00 |  |  |  |  |  |

| L            | 0.25            | 0.30        | 0.35 |  |  |  |  |  |

| h            | 0.15            | 0.20        | 0.25 |  |  |  |  |  |

| К            | 0.20            | 0.25        | 0.30 |  |  |  |  |  |